IWILDT-X光安检机FPGA图像数据排序算法实现

作者: / / 阅读人数:0

在传统的集装箱安检机数据采集传输系统中。控制芯片直接将ad采集的前端x射线探测器的数据传输到上位机中,然后上位机软件在对数据进行排序整理然后在进行图像数据的处理,这样不仅降低了上位机CPU增加了处理负担,而且降低了图像数据的处理速度,大大降低了集装箱安检机的安检效率;由武汉艾崴IWILDT -AN 10080设计利用FPGA的高速数据处理特性,通过对AD采集的前端双能x射线探测器的图像数据在双端口RAM中进行排序处理,然后通过以太网将排序好的图像数据传输到上位机中,这样不仅降低了上位机的cpu的占用率提高了上位机图像处理的速度,使集装箱安检机的实时性能得到更好的提高。

1 FPGA及双端口RAM介绍

1.1 FPGA 简介

FPGA的高速数据处理特性”,通过对AD采集的前FPGA是-种可编程芯片,主要应用与专用集成端双能X射线探测器的图像数据在双端口RAM中.电路的设计,FPGA内部逻辑资源丰富,可以使用硬进行排序处理,然后通过以太网将排序好的图像数件描述语言(Verilog或VHDL)根据需求对电路进行设计,然后通过编译综合,引脚分配后,通过JTAG或 AS将程序烧录至FPGA中实现功能电路。并且用这些简单的逻辑电路经过硬件编程后可以组成复杂的逻辑实现更高级的功能。FPGA具有抗干扰能力强,运行速度快,可进行多次擦出的优点[4]。

1.2双端口RAM

双端口RAM是在1个SRAM存储器上具有两套完全独立的数据线,地址线和读写控制线,并允许两个独立的系统同时对其进行随机性访问的存储器,即共享式多端口存储器。双端口RAM最大的特点是存储数据共享。用FPGA来实现双端口RAM的功能可以很好地解决并行性和速度问题,而且其灵活的可配置特性使得基于FPGA的双端口RAM易于进行修改、测试及系统升级,可降低设计成本,缩短开发周期[5]。

2集装箱安检机数据采集传输概述

目前大多数集装箱安检机数据采集传输流程大概都分为三步,首先通过由多个探测板组成的双能x射线探测器对穿透物体后的x射线能量进行采集,然后每个探测板在接收到x射线能量后会根据能量的衰减增益输出相应的像素值,像素值会以模拟电压值的形式输出到下一级,然后这些代表图像像素信息的模拟电压值通过模数转换芯片将模拟电压值转换成图像数字量送人到控制芯片,最后控制芯片将图像数据通过网口或其他通信方式将图像数据传输到上位机中,通过图像处理软件将图像数据处理形成图像以供安全检查使用[61。

3整体设计框架

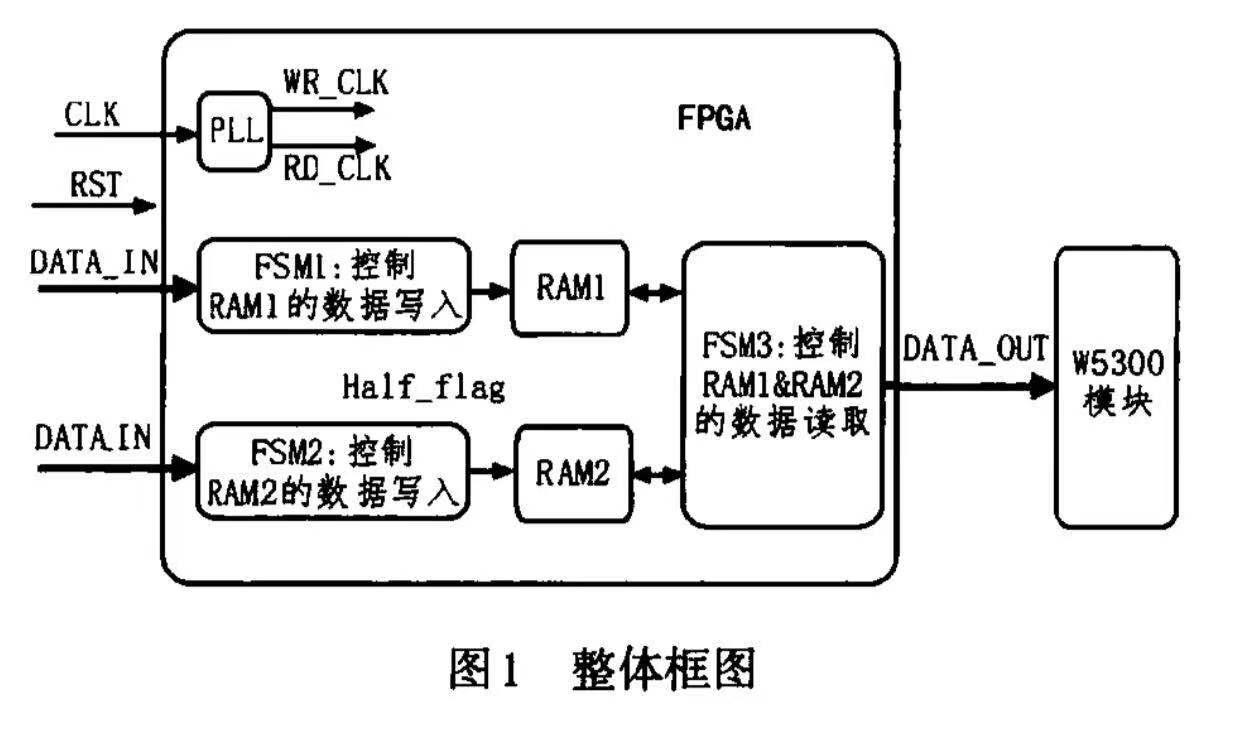

本设计主要利用FPGA中的双端口RAM核对两路AD采集到的图像数据进行数据排序然后传输到上位机。前端采用两个双能x射线探测器采集图像数据,每个探测器上最多可以连接8块探测板,每个探测板会输出128个像素值,其中包括先输出的64 个低能像素值和后输出的64个高能像素值。两路 AD分别对这两个双能x射线探测器所输出的高低能像素值进行模数软换为16位位宽的图像数据并送至FPCA,然后FPCA通过控制使图像数据能够按一定顺序存储在双端口RAM中以供后续通过网口或其他通信方式传输到上位机进行图像数据处理。由于本实现方法都在FPGA中实现,所以在 FPCA中主要通过两个双端口RAM以及RAM控制模块来实现图像数据的排序。首先对于前端两路数据输人分别通过两个RAM控制模块缓存到两个 RAM中并排序,然后通过一个读取RAM控制模块将两个RAM中的缓存数据读出,整体框图如图1所示。

3· 1双端口皿M核设计

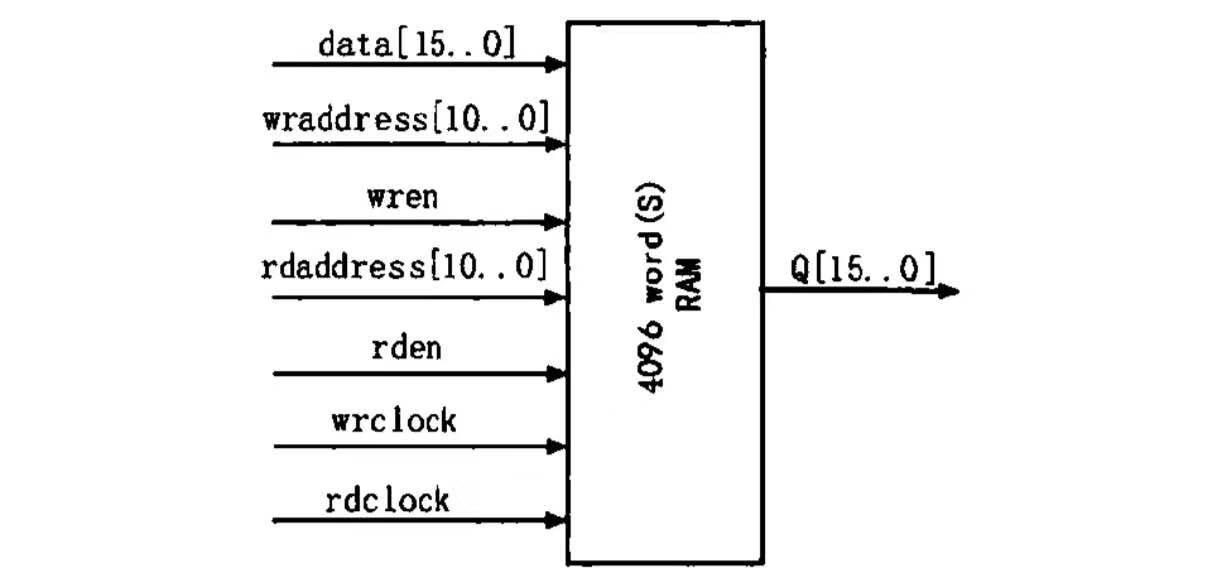

针对本集装箱安检机数据采集传输系统,将在FPGA 内部例化两个双端口RAM核,如此可以将两路AD 所采集的图像数据分别缓存到RAM中进行排序。由于AD所转换的是16位位宽数据,所以RAM的数据输人和输出端均为16位位宽,每一个AD所接前端探测器的探测板最多为8个,所以一次采集的图像数据大小最大为1 024个16位数据,为了在读取 RAM数据的同时前端图像数据还可以继续存人 RAM中,所以设置RAM核的深度为2048,地址总线宽度设置为11位位宽,由于设计中数据读出时钟是写人时钟的5倍,所以读时钟和写时钟均由PLL锁相环倍频得到。由于两路AD所采集的图像数据性质是一样的,所以在FPGA中例化的这两个双端口 RAM核所包含的引脚均一样,双端口RAM模块示意图如图2所示。

图2双端口RAM模块

引脚说明:data[ 15..0]为16位位宽数据输人端口;wraddress[10..0]为11位位宽写数据地址端口; wren为RAM写使能端口,高有效;rdaddress[10..0]为11位位宽读数据地址端口;rden为RAM读使能端口,高有效;wrclock为RAM写数据时钟端口; rdclock为RAM读数据时钟信号;q[15..0]为16位位宽数据输出信号。

3·2数据写入RAM控制模块

由于前端探测器所采集的数据的类型与排序方式是一样的,所以在这里只针对一路数据写人RAM 的控制模块进行阐述。首先根据前端x射线探测器所接探测板的数量的不同,AD持续采集数据的时间也会不同,例如ADI前端探测器接了3块探测板, AD2前端探测器接了4块探测板,那么两路AD同时开始采集图像数据,并且ADI在采集了3块探测板的图像数据之后要等待AD2采集完4块探测板之后再开始采集下一次的数据。

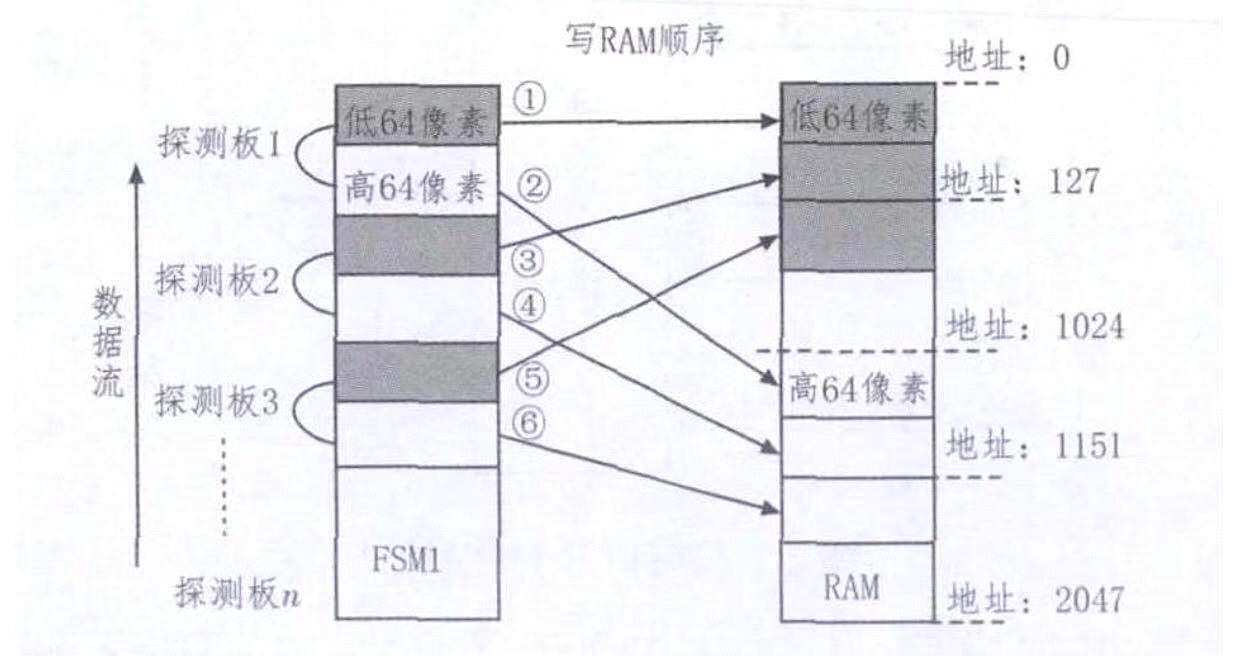

前端双能x射线探测器的每个探测板会输出 128个像素值,其中包含64个低能像素值和64个高能像素值,而最终要分别组成高低能两幅图像则首先要把每路的高低能像素值分段存储在RAM中。由于前端探测器所输出的顺序先是探测板1的64个低能像素值然后64个高能像素值,再然后是探测板 2的64个低能像素值然后64个高能像素值,所以数据写人RAM的控制模块中首先要将高低能像素值分别缓存到RAM的不同区域中以供后续取出。

当前端探测器数据开始采集之后,本模块首先将依次到来的探测板1的64个低能像素值依次存人到双端口RAM 1的0到63地址,随后将探测板1的 64个高能像素值依次缓存到双端口RAMI的1024 到1087地址;然后再将探测板2的64个低能像素值存人到RAMI的64到127地址,随后将探测板2的 64个高能像素值缓存到RAMI的1088到1巧1地址,并遵循此缓存规律将AD采集的高低能图像数据缓存到RAMI中,如图3所示。

3写RAM示意图

在将前端x射线探测器数据写人RAM的期间,因为前端接人探测板的数目不同,所以会导致其中一路优先全部写人RAM中,因此本设计编程思路是如果其中一个RAM将前端采集到的数据全部写人之后变监测另一路数据是否也全部写人RAM中,如果没有则等待,如果两路都已经缓存完毕则开始下一次的数据采集和缓存。并且数据写人RAM的地址会根据当前地址进行规律递增,当低能图像数据缓存到1 023地址后,下一低能图像数据将会0地址开始缓存,而高能图像数据缓存到2047地址后,下一个高能图像数据将会从1 024地址开始缓存。

3·3数据读出RAM控制模块

RAM读取的速率一般都比写人RAM的速率快,所以本设计用5倍于写人速率的读时钟来进行数据的读取。因此必须注意时钟追赶的问题,及读出一定要滞后写人,否则读出的数据就不是存人双端口 RAM的数据。因此本设计编程思想是在缓存一次前端探测器采集的数据之后发出可读数据标志位,然后数据读出RAM控制模块将这一次缓存的图像数据读出来,然后等待下一次的可读标志位。

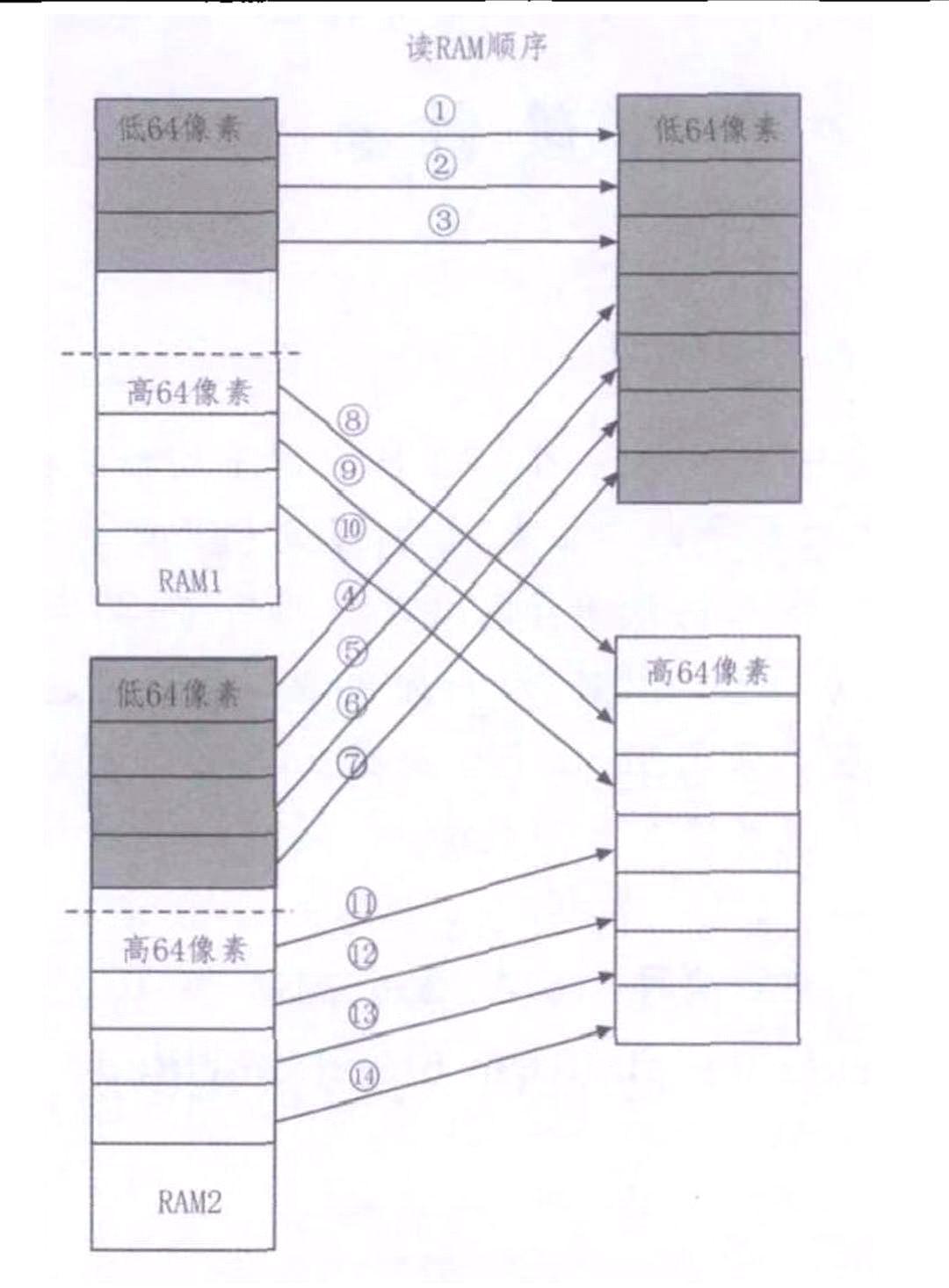

数据的读取就是将每一次所采集的所有低能图像数据和高能图像数据依次传输到上位机图像处理软件中进行处理,所以本设计先读取RAMI中的所有低能像素值,然后再读取RAM2中的所有低能像素值,再然后读取RAMI中的所有高能像素值,最后读取RAM2中的所有高能像素值;这样传输到上位机的图像数据先是一帧低能的图像数据然后是一帧高能的图像数据,如图4所示。

4仿真验证

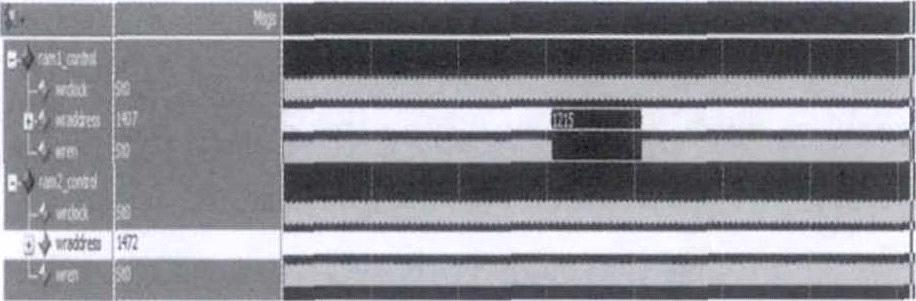

本设计模拟ADI前端双能x射线探测器接3个探测板,AD2前端双能探测器接4个探测板,所以仿真出来的信号如下图所示。控制RAMI写地址信号先从RAMI的地址0开始64个低能像素值,然后从地址1024开始写64个高能像素值,经过3次反复之后,写RAMI的最后一个地址会是1 2巧,之后会等待RAM2写完本次数据之后再开始写下一次数据,因为RAM2要缓存前端4个探测板采集的图像数据,所以RAM2会比RAMI多出写一个探测板采集的数据用的时间,当RAM2也将前端所采数据全部写完后,RAMI和RAM2会同时开始写人第二次采集的图像数据,因为前文所述,写RAM的地址会根据当前地址规律递增,所以当第二次也写完之后,RAMI的最后一个地址会是1407,如图5所示。

图5写RAM仿真图

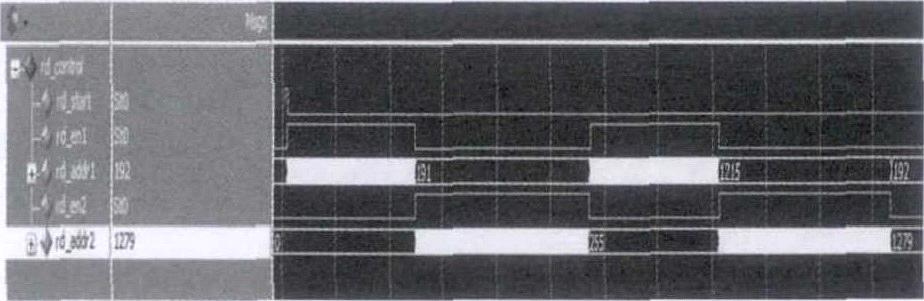

根据前文所述,读取RAM数据时首先要先读取 RAMI中所有低能像素值,由于ADI前端双能x射线探测器接了3个探测板,所以缓存低能数据的地址为0到191,然后再读取RAM2中所有低能像素值,而AD2前端双能x射线探测器接了4个探测板,所以缓存低能数据的地址为0到255,再然后读取 RAMI中所有的高能像素值,由于高能数据的缓存地址从1 024处开始,所以缓存高能数据的地址为 1 024到1 2巧,最后读取RAM2中所有的高能像素值,缓存地址为1024到1279,如图6所示。

图6读RAM仿真图

当今社会集装箱安检机的应用越来越广泛,为了更好地保证公共安全,同时又不降低生活效率,人们对集装箱安检机的要求也越来越高。武汉艾崴为了提高集装箱安检机数据采集传输速率,本文从图像数据的排序人手,利用 FPGA的高速数据处理特性,并通过FPGA内部的存储单元(M4K、M9K等)构造双端口RAM,将前端采集到的图像数据进行排列整齐以供上位机图像处理软件使用。用FPCA内部存储器构造双端口RAM不仅节省了大量逻辑,而且也为下级数据的读取提供了友好的时序控制。因此利用FPGA对前端探测器采集的图像数据进行排序不仅简化了下级数据读取控制逻辑而且提高了上位机图像处理速度。